First look at the digital circuit, understand what is right and wrong, various triggers, various logic gates, pay attention! You can understand it, but how it works must be thorough and thorough! (The FPGA uses the HDL, which is the hardware description language. The program is used to describe your logic gates. The digital power is the foundation!) The book's words I look at is the electronic technology foundation (digital part) Kang Huaguang's book also comes with verilog Introduction to language!

Look at the book of FPGA design and application class again, understand FPGA this device in detail, why it is born, why popular, characteristic, shortcoming. If you have English skills, you can directly look at English on the official website. Like ALTERA, XILINX, these two websites are all big NB's. No skill, see FPGA design and application Xi'an University of Electronic Science and Technology Press is very detailed. Can be checked as a manual, so long has not been lost in my drawer.

Look again at VHDL, or verilog language books.

There are differences here. The former has strict grammar. It is suitable for large-scale systems and is difficult to get started. However, it has learned a deeper understanding of the hardware structure.

The latter is adapted from the C language. If you have a C language foundation, learning this is easy to use. The disadvantage is that the system level description is not correct. It follows the flexibility of the C language, and it also brings grammatical non-strict, but its role is wide, novice Recommended, the underlying description is very good.

Here I use VHDL, can only recommend VHDL hardware description language VHDL tutorial Xi'an Jiaotong University Press Jiang Xuesong

If you learn verilog, it's best to take a look at the C language book. The basics must be firm. Otherwise, the code will scale, and you will be tragedy. Looking back is hard!

Look at the use of HDL design software book I use the QUARTUS II software, looks like the most popular is the software, this book, as a manual on the line, mainly to introduce how to use the software, tell you how to build the project, how to enter Procedures, drawing schematics, compile error correction, timing simulation, all here, the software used is better than the difference between using a great deal! When you don’t, you’re going crazy.

Here just to buy what kind of book on the OK, online search FPGA system design and examples, a lot.

If you want to crash, then watch the video on the Internet. This is mainly for applications. Let your board run in an hour. The quick rise in the early days and the invigoration of the use of science means that there will be no systematic theoretical support in the later period and it will be a bit laborious. Especially for large projects, it is completely a tragedy. What I can do in China is Zhou Ligong. Amy Electronics can do it. Both have learning boards, but the latter's tutorial plagiarizes the former. The former has a deeper foundation of knowledge. If the funds are not tight, buy the former. If it is fast, then the number of books must be necessary. It is better to watch while studying. The rest of the books can be bought in moderation.

So many, in fact, as long as you are interested, learn slowly, entry is not difficult, the board went online shopping.

Let's talk about FPGA basic knowledge first:FPGA (Field-Programmable Gate Array), field programmable gate array, which is the product of further development based on PAL, GAL, CPLD and other programmable devices. It appears as a semi-custom circuit in the field of application-specific integrated circuits, which not only solves the deficiency of the custom circuit, but also overcomes the shortcomings of the limited number of original programmable devices.

1, the basic principles of hardware design

(1) Balance and interchange principle of speed and area: If a design has a large timing margin, the frequency it can run is much higher than the design requirements, and the chip area consumed by the entire design can be reduced through module multiplexing. Speed ​​advantage for area saving; conversely, if a design of the timing requirements are high, the ordinary method can not reach the design frequency, then you can use the data stream string and convert, copy multiple operating modules in parallel, the entire design using "ping pong operation" The idea of ​​“serial-to-parallel conversion†is handled, and the data is “parallel converted†at the output module of the chip. In order to achieve the use of area copy exchange speed.

(2) Hardware principles: Understanding the nature of HDL

(3) System principle: overall grasp

(4) Synchronous Design Principles: Basic Principles for Stable Design Timing

2. As an HDL language, Verilog has hierarchical modeling of system behavior. The more important levels are system level, algorithm level, register transfer level, logic level, gate level, and circuit switching level.

3, in the actual work, in addition to the use of for loop statements to describe the simulation test excitation, rarely use the for loop in the RTL level coding, this is because the for loop will be expanded by the synthesizer to execute the statement of all variables, each variable Independently occupying register resources cannot effectively multiplex hardware logic resources, causing huge waste. Generally used case statements instead.

4. If...else... and case are very different in the nested description, if...else... is prioritized. In general, the first if has the highest priority and the last has the lowest priority. . While the case statement is a parallel statement, it has no priority, and the establishment of the priority structure requires a lot of logic resources, so if you can use the case, do not use the if...else... statement.

Supplement: 1. You can also use if...; if...; if...; to describe "parallel" statements without precedence.

5, FPGA general trigger resources are more abundant, and CPLD combination logic resources are more abundant.

6, FPGA and CPLD composition:

FPGA basically consists of six parts: programmable I/O unit, basic programmable logic unit, embedded block RAM, abundant wiring resources, underlying embedded functional unit, and embedded dedicated hard core.

The structure of CPLD is relatively simple, mainly composed of programmable I/O unit, basic logic unit, wiring pool and other auxiliary function modules.

7, Block RAM:

Three kinds of block RAM structure, M512 RAM (512bit), M4K RAM (4Kbit), M-RAM (64Kbit).

M512 RAM: Suitable for some small Buffer, FIFO, DPRAM, SPRAM, ROM, etc.

M4K RAM: Suitable for general needs

M-RAM: A buffer suitable for large blocks of data.

The LUTs of Xlinx and LatTIce FPGAs can be flexibly configured into small RAM, ROM, FIFO, and other storage structures. This technology is called distributed RAM.

Supplement: However, in the general design, it is not recommended to use FPGA/CPLD's on-chip resources to configure a large amount of memory, which is a cost consideration. So try to use external memory.

8, make good use of the chip's internal PLL or DLL resources to complete the clock frequency, frequency, shift the same operation, not only simplifies the design, and can effectively improve the system's accuracy and job stability.

9, the difference between asynchronous circuit and synchronous sequential circuit

Asynchronous circuit:

Circuit core logic is useful for combinational circuit implementation;

The biggest drawback of asynchronous sequential circuits is that they are prone to glitches.

Not conducive to device transplantation;

Not conducive to static timing analysis (STA), verify the design timing performance.

Synchronous timing circuit:

Circuit core logic is implemented using various flip-flops;

The main signal, output signal, etc. of the circuit are all generated at a certain clock edge driving flip-flop;

Synchronous timing circuit can be very good to avoid glitches;

Facilitate device migration;

It facilitates static timing analysis (STA) and validates design timing performance.

10. In the synchronous design, stable and reliable data sampling must comply with the following two basic principles:

(1) Before the effective clock edge arrives, the data input has at least stabilized the setup time of the sample register. This principle is abbreviated to satisfy the principle of Setup time;

(2) After the valid clock edge arrives, the data input will at least stably hold the Hold clock of the sampling register. This principle is referred to as the Hold time principle.

11, synchronous timing design considerations:

Asynchronous clock domain data conversion.

Combinational logic circuit design method.

Clock design for synchronous timing circuits.

Synchronization timing circuit delay. The most common design method for the delay of the synchronous timing circuit is to use a clock or a frequency-divided clock or a synchronous counter to complete the required delay. In contrast to the large and special timing required delay, a counter is generally generated with a high-speed clock, according to the count. Delay is generated; for relatively small delays, it can be triggered by a D flip-flop, which not only delays the signal by one clock cycle, but also completes the initial synchronization of the signal with the clock. Used for input signal sampling and increasing timing constraint margins. In addition, there are behavioral methods to describe the delay, such as "#5 a "=4'0101;" This is often used to simulate the test excitation, but will be ignored in the circuit synthesis, and can not play a delay.

The reg types defined by Verilog are not necessarily synthesized into registers. The two most commonly used data types in Verilog code are wire and reg types. In general, wire-specified data and net lines are implemented using combinatorial logic, and reg-type data is not necessarily implemented using registers.

12, common design ideas and techniques

(1) Ping Pong operation;

(2) Serial-to-parallel conversion;

(3) assembly line operation;

(4) Asynchronous clock domain data synchronization. This refers to the problem of how to reliably exchange data between two clocks that are out of sync. There are two main situations when the data clock domain is out of sync:

The clock frequencies of the two domains are the same, but the difference is not fixed, or the difference is fixed but not measurable. It is referred to as the out-of-phase problem of the same frequency.

The two clock frequencies are fundamentally different, referred to as the inter-frequency problem.

Two deprecated asynchronous clock domain operation methods: One is to adjust the sampling by increasing the Buffer or other gate delay; the other is to blindly use the positive and negative edges of the clock to adjust the data sampling.

13, the basic principle of module division:

(1) Registers are used for the output of the sub-modules of each synchronous timing design (regarding the principle of dividing the synchronous timing module by registers).

(2) Divide related logic and reusable logic in the same module (echo system principle).

(3) Separate the logic of different optimization goals.

(4) The logic of sending constraints is assigned to the same module.

(5) Separate storage logic into modules.

(6) The appropriate module size.

(7) The top level module is preferably not logically designed.

14, the combination of logic considerations

(1) Avoid combinatorial logic feedback loops (easily glitches, oscillations, timing violations, etc.).

solve:

A. Keep in mind that any feedback loop must include registers;

B. Check the synthesis, and implement the warning information of the report, and find that the feedback loop (combinaTIonal loops) is modified accordingly.

(2) Replace the delay chain.

Solution: Complete with frequency multiplication, frequency division, or synchronization counter.

(3) Replace the asynchronous pulse generating unit (glitch generator).

Solution: Design the pulse circuit with synchronous timing.

(4) Use latches with caution.

solve:

A, use the complete if...else statement;

B. Check whether the design contains a combinational logic feedback loop;

C. For each input condition, design the output operation and set the default operation for the case statement. Especially in the state machine design, it is better to have a default state transition, and each state preferably also has a default operation.

D. If you use the case statement, especially when designing the state machine, try to add the comprehensive constraint attributes and synthesize the complete condition case statement.

Tip: Carefully check the comprehensive report of the integrator. Most synthesizers currently report “warning†to the synthesized latch. It is easier to find out the accidentally generated latch through the comprehensive report.

15, the clock design considerations

(1) The recommended clock design method for synchronous sequential circuits:

The clock is input via the global clock input pin, and is frequency-divided/multiplied, shifted and equal-adjusted by the dedicated PLL or DLL within the FPGA, and then driven to the clock input of all registers and other modules in the chip via the global internal clock routing resources of the FPGA. end.

FPGA designer's five basic skills: simulation, synthesis, timing analysis, debugging, verification.

For FPGA designers, to practice these five basic skills is the same process as using the appropriate EDA tools. The corresponding relationship is as follows:

1. Simulation: Modelsim, Quartus II (Simulator Tool)

2. Synthesis: Quartus II (Compiler Tool, RTL Viewer, Technology Map Viewer, Chip Planner)

3. Timing: Quartus II (TImeQuest TIming Analyzer, Technology Map Viewer, Chip Planner)

4. Debug: Quartus II (SignalTap II Logic Analyzer, Virtual JTAG, Assignment Editor)

5. Validation: Modelsim, Quartus II (Test Bench Template Writer)

Mastering HDL language is not all of FPGA design, but the impact of HDL language on FPGA design runs through the entire FPGA design flow. The five basic functions of FPGA design are complementary.

For FPGA designers, 50% of FPGA design can be done using the “scalable subset of HDL languageâ€â€”design coding.

The three basic skills of simulation, synthesis, and timing analysis are well-developed, which helps to learn “a comprehensive subset of HDL languageâ€:

1. Through simulation, you can observe the logical behavior of the HDL language in the FPGA.

2. Through synthesis, you can observe the physical implementation of HDL language in FPGA.

3. Through timing analysis, you can analyze the physical implementation of HDL language in FPGA.

For FPGA designers, using the "verified sub-set of HDL language" can complete another 50% of the FPGA design - debug verification.

1. Build a verification environment and verify the correctness of the FPGA design by means of simulation.

2. Comprehensive simulation verification can reduce the workload of FPGA hardware debugging.

3. Combine hardware debugging and simulation verification methods, use debugging to solve unverified problems of simulation, use simulation to ensure that the problems that have been solved are not reproduced in debugging, and a regression verification flow can be established to facilitate the maintenance of FPGA design projects.

The five basic functions of FPGA designers are not isolated and must be used together to complete a complete FPGA design process. Conversely, by completing a complete design process, these five basic skills can be most effectively exercised. With a preliminary understanding of these five basic skills, you can learn more about each one, and then apply the learned knowledge to the complete design process again. If so, you can gradually increase the level of design. With such a gradual and spiraling approach, as long as you enter the door through training, you can self-learn and self-improvement.

The books on FPGA design sold on the market are designed to ensure the integrity of the structure. Each aspect of FPGA design is introduced separately. Although every aspect is in-depth, due to the lack of other related aspects, readers can hardly put it into practice. Only read through the books. A complete book can gain a general understanding of FPGA design. Such a book, as an engineering training guide, cannot be used as an advanced reference book for a certain aspect.

For newly recruited employees, they often have a preliminary understanding of the overall design flow of the FPGA. Some aspects of the five basic skills may be very solid. However, due to lack of ability in one or several aspects, they have limited their ability to complete the entire design process. The purpose of on-the-job training is to help them master the overall design process, cultivate their self-acquisition capacity, train back and forth through several design processes, and form a virtuous cycle of self-promotion and self-development. In this process, as the knowledge of the breadth and depth of knowledge involved in the work becomes clear and clear, new employees’ self-confidence will gradually increase, and the direction of individual development will gradually be clear so that they can actively participate in the project. Come in.

Final summary of several points:

1) Look at the code and build the model

Only by establishing a logical model in the mind and understanding the basics of the logic structure in FPGA, can we understand why writing Verilog and writing C are not the same in their overall thinking, so that we can understand the differences in the design method of sequential execution language and parallel execution language. . When you see a simple program, you should think of what kind of functional circuit it is.

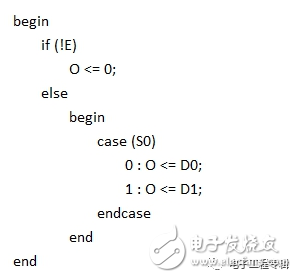

E.g:

2) Use mathematical thinking to simplify design logic

Learning FPGAs is not only a matter of logical thinking. Good mathematics thinking can also simplify your design. Therefore, those children who see high numbers of headaches need to pay attention to this course. For a simple example, there are two 32-bit data X[31:0] and Y[31:0]. Of course, both Altera and Xilinx have ready-made multiplier IP cores that can be called. This is the simplest method, but the two 32-bit multipliers will consume a lot of resources. So is there a way to save resources and not a complicated way to achieve it? We can modify it slightly:

Split X[31:0] into two parts X1[15:0] and X2[15:0] and let X1[15:0]=X[31:16],X2[15:0]=X[15 : 0], then X1 is shifted left by 16 bits and added to X2 to get X; Similarly, Y[31:0] is split into two parts Y1[15:0] and Y2[15:0], letting Y1[15: 0]=Y[31:16],Y2[15:0]=Y[15:0], then Y1 is shifted left by 16 bits and added to Y2 to get Y; then the multiplication of X and Y can be converted to X1 X2 is multiplied by Y1 and Y2, respectively, so that a 32-bit*32-bit multiplication operation is converted into four 16-bit*16-bit multiplication operations and three 32-bit addition operations. After the conversion, the occupied resources will be reduced a lot. If you are interested in children's shoes, you may want to take a look at it and see how bad it is.

3) The relationship between clock and trigger

The phrase "the clock is the controller of the sequential circuit" is too classic. It can be said that it is a word of FPGA design. The design of the FPGA is mainly based on sequential circuits, because the combinational logic circuit can not be much complicated and how difficult it is to understand. But the timing circuit is different. All its actions are triggered when the clock beats. It can be said that the clock is the controller of the entire circuit. If the control is not good, the circuit function will be confused.

For example, the clock is equivalent to the heart of the human body. Every time it beats, it triggers a CLK. It supplies blood to various organs of the body and maintains the normal operation of the body. Every organ system can work normally without the formation of tissue cells. The device can be compared to the basic unit tissue cells. The clock of the sequential logic circuit is the "engine" that controls the state transition of the sequential logic circuit. Without it, the sequential logic circuit can not work normally, because the sequential logic circuit mainly uses the state of the flip-flop memory circuit, and the flip-flop state transition needs the rise of the clock. Or falling edge! This shows the core role of the clock in the sequential circuit!

In the end, simply talk about it, and in the end, you will practice, think, and ask more. Practice knowing and looking at other people’s programs 100 times is not as good as practice. The motivation of practice comes from the interest on the one hand and the pressure on the other. I personally feel that the latter is more important. Demand can easily become stressful, which means it is best to practice in actual project development rather than to learn. In the process of practice, we must think more and think more about the reasons for the problems. After the problems are solved, we must ask them a few more questions. This is also the process of experience accumulation. If there is a better habit of writing project logs, we need to solve problems and causes. The methods are written in. Finally, we must ask more questions. We must ask questions after we encounter problems. After all, the power of individuals is limited. Ask classmates, ask search engines, and ask netizens. It may help you solve the problem quickly.

Optical Rotary Sensor,Custom Encoder,Optical Encoder 6Mm Shaft,Handwheel Pulse Generator

Jilin Lander Intelligent Technology Co., Ltd , https://www.jilinlandermotor.com