GPIO----"General Purpose Input/Output Port" ---- is a flexible software controlled digital signal. Many types of chips are available, and embedded linux developers and hardware customizers will be familiar with this. Each GPIO provides one bit for connection to a specific pin (or "ball" under the BGA (BallGridArray) package). The board schematic shows the connection between external hardware and GPIOs. The GPIO driver can be written generically so that the board setup code can pass these pin configuration data to the driver.

The SOC processor is very dependent on GPIO. In some cases, common pins can be configured as GPIOs. Most chips have at least several groups of similar GPIOs. Programmable logic devices (such as FPGAs) can easily provide GPIO. Some multifunctional chips, such as power management, voice decoding, etc., often have some such pins to compensate for the lack of pins on the SOC chip. Similarly, there are also some GPIO expansion chips connected to the I2C or SPI serial bus. Most PC South Bridges have several sets of GPIO-compatible pins (only the BIOS firmware knows how to use them).

The exact role of GPIO between different systems is different. Commonly used are the following:

----Output value can be written (high = 1, low = 0). Some chips may also choose to drive these values ​​in a way that supports "line-or" or similar schemes (open-drain signal lines).

---- The input value is readable (1,0). Some chips support readback of the output pins, which is very useful in an online or in case (to support bidirectional signal lines). The GPIO controller may have an input failsafe/anti-bounce logic and sometimes software control.

The input is often used as an interrupt signal, usually an edge trigger, but it may also be a level trigger. These interrupts can be configured as system wake-up events to wake up the system from low-power modes.

---- A GPIO is often configured as input / output bidirectional, depending on the needs of different product boards, but there is also a one-way situation.

Mostly GPIOs can be accessed when spinlock spinlocks are acquired, but those that are accessed through a serial bus typically cannot do so (the cause of hibernation). Some two types of GPIOs exist in some systems.

On a given board, each GPIO is used for a specific purpose, such as monitoring the insertion/removal of the MMC/SD card, checking the card write protection status, driving the LEDs, configuring the transmitter, and serial bus bits Split, trigger a hardware watchdog, trigger a switch and the like.

Second, the advantages of GPIO (port expander)Low power consumption: GPIO has lower power consumption (approximately 1μA, μC operating current is 100μA).

Integrated IIC Slave Interface: The GPIO has a built-in IIC slave interface that operates at full speed even in standby mode.

Small Package: GPIO Devices Offer the Smallest Package Size - 3mm x 3mm QFN!

Low cost: You don't have to pay for unused features.

Fast time to market: No need to write additional code, documentation, and no maintenance.

Flexible light control: Built-in multiple high-resolution PWM outputs.

Predetermined response time: Shorten or determine the response time between an external event and an interrupt.

Better light effects: Matched current output ensures uniform display brightness.

The wiring is simple: only 2 can be used to form the IIC bus or 3 SPI buses.

Similar to several groups of GPIO pins of ARM, GPxCON controls the function of pins, and GPxDAT is used to read and write pin data. In addition, GPxUP is used to determine if pull-up resistors are used. x is A, B,, H/J,

GPAUP does not have a pull-up resistor.

Third, GPIO hardware introduction 1. Through the register to operate GPIO pinGPxCON is used to select the pin function and GPxDAT is used to read/write the pin data. In addition, GPxUP is used to determine whether an internal pull-up resistor is used. x is B,. . ., H/J, no GPAUP register.

1.1 GPxCON register

As can be seen from the register name, it is used to configure - select the pin function.

PORTA differs from PORTB~PORT H/J in function selection. Each bit in GPACON corresponds to one pin (23 pins in total). When a bit is set to 0, the corresponding pin is an output pin. At this time, we can write 0 or 1 to the corresponding bit in GPADAT to make this pin low or high; when a bit is set, When 1, the corresponding pin is the address line or is used for address control, at this time GPADAT useless. In general, GPACON is usually set to all 1s in order to access external memory devices.

PORT B~ PORT H/J are identical in register operation. Each bit in GPxCON controls one pin: 00 means input, 01 means output, 10 means special function, 11 is not used.

1.2 GPxDAT register

GPxDAT is used to read/write the pin; when the pin is set as input, reading this register shows the corresponding pin's level status is high or low; when the pin is set to output, writing the corresponding bit of this register can make This pin outputs high or low.

1.3 GPxUP register

GPxUP: When a bit is set to 1, the corresponding pin has no internal pull-up resistor; when it is 0, the corresponding pin uses an internal pull-up resistor.

The role of the pull-up resistor is: When the GPIO pin is in the third state (that is, not the output high, nor the output low, but a high-impedance state, which is equivalent to not connected to the chip), its level The state is determined by pull-up resistors and pull-down resistors.

2, access to hardware2.1 Access to a Single Pin

The operation of a single pin is nothing more than three: output high and low, detect the pin state, interrupt. The operation of a pin is usually done by reading and writing registers.

Access to these registers is by software to read and write their addresses. For example, the GPBCON and GPBDAT register addresses of the S3C2410 and S3C2440 are 0x56000010 and 0x56000014. You can use the following instruction to make the GPB5 output low level.

#define GPBCON (*volaTIle unsigned long *)0x56000010) //long=int 4 bytes; char 1 byte; short 2 bytes

#define GPBDAT (*volaTIle unsigned long *)0x56000014)

#define GPB5_out (1 "(582))

GPBCON = GPB5_out;

GPBDAT &= ~(1 "5";

2.2 Bus Access to Hardware

It is not only through the register that the hardware signal can be sent. In fact, controlling the hardware by accessing the bus is more common. As shown in the following figure, the connection diagrams of S3C2410/S3C2440 and NOR Flash are read and write operations in 16-bit units.

The role of the buffer in the figure is to improve the drive capability and isolate the signals before and after the stage. The chip select signal of NOR Flash (AM29LV800BB) uses the nGCS0 signal. When the address signal sent by the CPU is between 0x00000000 and 0x07FFFFFF, the nGCS0 signal is valid (low level), and NOR Flash is selected. At this time, the CPU sends an address signal to the NOR Flash; during a write operation, the nWE signal is low and the data signal is sent from the CPU to the NOR Flash; during a read operation, the nWE signal is high and the data signal is sent from the NOR Flash to the CPU. .

ADDR1~ADDR20 ------------------" "--------------------A0~A19

DATA0~DATA15 "-----------------" "-------------------" D0~D15

nOE ------------------" --------------------"nOE

nWE ------------------" --------------------"nWE

nGCS0 ------------------" --------------------"nCE

S3C2410/S3C2440 Buffer NOR Flash (AM29LV800BB)

How the software initiates the write operation, there are several examples of code to explain.

1) Address aligned 16-bit read operation

Unsigned short *pwAddr = (unsigned short *)0x2;

Unsigned short uwVal;

uwVal = *pwAddr;

The above code will initiate a read operation to the NOR Flash: the read address sent by the CPU is 0x2, and the signals of the address buses ADDR1~ADDR20 and A0~A19 are all 1,0. . , 0 (CPU's ADDR0 is 0, but ADDR0 is not connected to NOR Flash). The NOR Flash address is 0x1. NOR Flash takes the 16-bit data from the address at a later time and sends it to the CPU via data bus D0~D15.

2) 16-bit read operation with address bit misalignment

Unsigned short *pwAddr = (unsigned short *)0x1;

Unsigned short uwVal;

uwVal = *pwAddr;

Since the address is 0x1, it is not 2-aligned, but the bit width of BANK0 is set to 16, which will cause an exception. We can set up an exception handler to handle this situation. In the exception handling function, use 0x0, 0x2 to initiate two read operations, and then combine the two results: use two bytes of data D0, D1 at address 0x0; then use address 0x02 to read D2, D3; and finally, D1 D2 is combined into a 16-bit number returned to wVal. If there is no address misalignment exception handler, then the above code will be wrong. If the bit width of a BANK is set to n, address-aligned n-bit operations will always be seen on the bus when accessing this BANK.

3) 8-bit read operation

Unsigned char *pwAddr = (unsigned char *)0x6;

Unsigned char ucVal;

ucVal = *pwAddr;

The CPU first uses the address 0x6 to initiate a 16-bit read operation on NOR Flsh to get two bytes of data, assuming D0, D1; then the D0 is assigned to the variable ucVal. During the read operation, the signals of the address buses ADDR1~ADDR20, A0~A19 are 1, 1, 0, and . . ., 0 (CPU's ADDR0 is 0, but ADDR0 is not connected to NOR Flash). The CPU automatically discards D1.

4) 32-bit read operation

Unsigned int *pwAddr = (unsigned int *)0x6;

Unsigned int udwVal;

udwVal = *pwAddr;

The CPU first uses the address 0x6 to initiate a 16-bit read operation on NOR Flsh to obtain two bytes of data, assuming D0, D1; and then use the address 0x8 to initiate a read operation to obtain two bytes of data, assuming D2, D3; Finally, these four data are combined and assigned to the variable udwVal.

5) 16-bit write operation

Unsigned short *pwAddr = (unsigned short *)0x6;

*pwAddr = 0x1234;

Due to the nature of the NOR Flash, the write operation of the NOR Flash is complicated - for example, a specific address signal is first sent to inform the NOR Flash to receive data, and then the data is sent out. However, the relationship between the electrical signals on the bus and the software instructions is similar to the read operation except that the data is transmitted in the opposite direction.

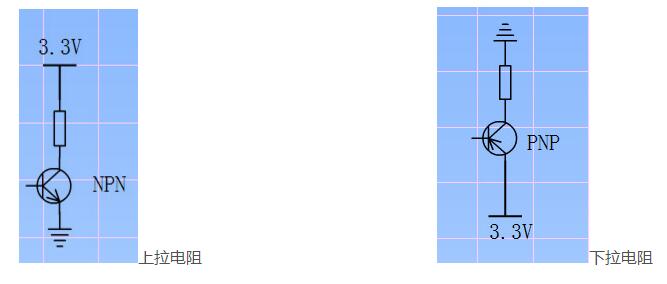

Fourth, what is the pull-up resistor, pull-down resistorThe pull-up resistor is for NPN and the pull-down resistor is for PNP! Whether it is pull-up resistor or pull-down resistor is to make sure that the collector has a certain potential!

For example, for NPN, when the pull-up resistor is not used, if the base set is positive, it is turned on and the collector is 0. But when the base set is 0, it is cut off. At this time, the collector is floating and the potential cannot be determined! Once a pull-up resistor is added, the collector is 0 when turned on, and the collector is positive when off.

Similarly for PNP, the collector is positive when turned on, and the collector is 0 when it is off.

The operation of a single pin is nothing more than three cases: output high and low, detect the pin state, interrupt. The operation of the pin is generally completed through the configuration of a specific register.

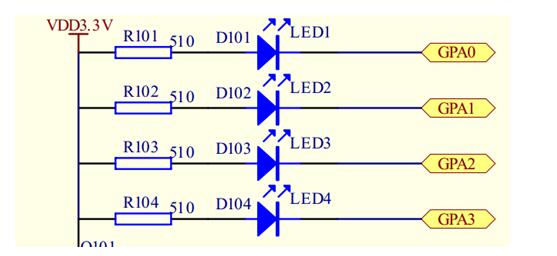

As shown in the figure, according to the hardware circuit diagram of the LED, light up the LED:

[cpp] view plaincopy#define GPFCON (*(volaTIle unsigned long *)0x56000050)

#define GPFDAT (*(volaTIle unsigned long *)0x56000054)

#define GPF4_out (1 "(4*2))

#define GPF5_out (1 "(5*2))

#define GPF6_out (1 "(6*2))

#define GPF7_out (1 "(7*2))

Void wait(volatile unsigned long dly)

{

For(; dly ) 0; dly--);

}

Int main(void)

{

Unsigned long i = 0;

GPFCON = GPF4_out|GPF5_out|GPF6_out|GPF7_out; // Set three pins of LED1-4 corresponding to GPF4/5/6/7 as output

While(1){

Wait(30000);

GPFDAT = (~(i "4"); // Light LED1~4 according to the value of i

If(++i == 8)

i = 0;

}

Return 0;

}

All In One Business Computer is the one of the important All In One PC series, can meet all enter and normal business application scenarios. Therefore, more and more clients choose and recommend this Business All In One Computer for business or education projects. The Best All In One Computer For Business is the similar Apple design, competitive and attractive, the hottest parameters is 19 or 21.5 inch intel i3 or i5 2th or 3th or 4th 4 gb ram 128GB ssd . There are many other all In One Computers For Business with lighter weight. Of course, you can see Colorful All In One Gaming PC, All In One Desktop Touch Screen and All In One Business Pc. Believe you can always find the right one at this store. To save time, You can also contact us by email or calling directly to get matched and valuable information fast.

Any other special configuration interest, also feel free to let us know, will try our best to back you up.

Except all in one Custom All In One PC, 14 inch Education Laptop and 15.6 inch business laptop also available here.

All In One Business Computer,Business All In One Computer,Best All In One Computer For Business,all In One Computers For Business,All In One Business Pc

Henan Shuyi Electronics Co., Ltd. , https://www.shuyioemminipc.com