In today's world, high-tech handheld devices are widely popular, you might think that parallel data interface is an outdated thing. After all, this architecture has been on the market for decades, and it is no longer regarded as a candidate for future development in today's market that focuses on small size, low power consumption, and rich functions. However, there are still many new mobile phone and MID designs that continue to use this old interface because it is the only available interface for the application processor.

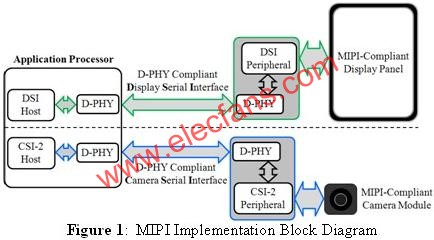

Currently, the end market requires new designs with lower power consumption, higher data transmission rates and smaller PCB footprints. Under this huge pressure, some intelligent alternatives with higher performance and price ratios have begun to gradually Used by relevant designers. Among several standards-based serial differential interfaces currently in use, MIPI interfaces have grown extremely rapidly in the field of mobile handheld devices that are power sensitive and require high performance. The broad adoption of baseband and display / camera modules for the MIPI Display Serial Interface (DSI) and Camera Serial Interface (CSI-2) protocols is the main driver of this growth. DSI and CSI-2 are logical-level protocols required for monitors and cameras, respectively. They manage, error, and communicate data between the host and peripheral devices through physical interconnections. MIPI D-PHY specifies the physical and electrical characteristics of the physical layer connecting the processor and peripherals. These MIPI interfaces are specifically designed to serve the mobile device market. Figure 1 shows a schematic diagram of the top module of the MIPI interface between the display and the camera.

Figure 1: Schematic diagram of the MIPI implementation solution module

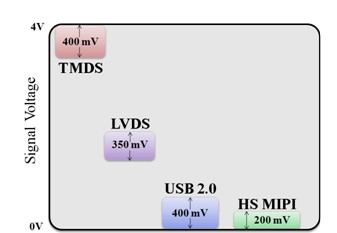

Here are two examples of large-scale adoption of MIPI, including two major chipset manufacturers Intel (Intel) and Marvell have integrated MIPI functions in their latest mobile chip architecture, Intel ’s Moorestown processor and Marvell ’s Armada 600 The processors all use the DSI or CSI interface based on the MIPI standard. The MIPI architecture can reduce the number of pins and power consumption of the processor by reducing the number of I / Os in its differential serial interface, so it is the best choice to let it go. Dynamically adjustable low-power (LP) and high-speed (HS) data modes and low signal swing in high-speed mode can also provide MIPI with better EMI radiation performance and EMI immunity than single-ended interfaces performance. In addition, due to the reduction of wiring, PCB design flexibility is improved, which can improve the layout of connectors or peripheral devices. Although these advantages are common to many serial interfaces, MIPI is specifically tailored for power-sensitive applications with low-amplitude signal swings in high-speed (data transmission) mode. Figure 2 compares the signal swing of MIPI and other differential technologies.

Figure 2: Comparison of signal amplitudes of several popular differential-swing (differenTIal-swing) techniques

Another major feature of this architecture is scalability. MIPI stipulates a differential clock channel (lane) and a extensible number of data channels from 1 to 4. The data rate can be adjusted according to the needs of processors and peripherals. Moreover, the MIPI D-PHY specification only gives a data rate range, and does not specify a specific operating rate. In an application, the available data channels and data rates are determined by the devices at both ends of the interface. However, the currently available MIPI D-PHY IP core can provide a transmission rate of up to 1 Gbps per data channel, which undoubtedly means that MIPI is fully suitable for current and future high-performance applications.

The use of MIPI as a data interface has another major benefit. Because MIPI DSI and CSI-2 architectures bring flexibility to new designs and support impressive features such as XGA displays and cameras above 8 megapixels, MIPI is very suitable for new smartphone and MID designs. With the bandwidth capabilities provided by the new processor design with MIPI capabilities, it is now possible to consider using a single MIPI interface to implement novel features such as high-resolution dual-screen display and / or dual cameras.

In designs that use these features, high-bandwidth analog switches designed and optimized for MIPI signals, such as Fairchild Semiconductor ’s FSA642, can be used to switch between multiple displays or camera components. FSA642 is a high-bandwidth three-way differential single-pole double-throw (SPDT) analog switch that enables one MIPI clock channel and two MIPI data channels to be shared between two peripheral MIPI devices. Such switches can provide some additional advantages: to isolate stray signals (stubs) of unselected devices, and to increase the flexibility of wiring and peripheral layout. In order to ensure the successful design of these physical switches on the MIPI interconnect path, in addition to bandwidth, the following main switch parameters must also be considered:

1. Shutdown isolation: In order to maintain the signal integrity of the active clock / data path, the switch is required to have efficient shutdown isolation performance. For high-speed MIPI differential signals of 200mV and maximum common-mode mismatch of 5mV, the turn-off isolation between the switch paths should be -30dBm or better.

2. Differential delay difference: The delay difference between the internal signals of the differential pair (skew) (the difference within the differential pair) and the delay difference between the clock and data channel differential crossing points (the difference between the channels) must be reduced to 50 ps or more small. For these parameters, the industry's best-in-class delay difference performance for this type of switch is currently between 20 ps and 30 ps.

3. Switch impedance: When choosing an analog switch, the third major consideration is the trade-off between the impedance characteristics of the on-resistance (RON) and the on-capacitance (CON). The MIPI D-PHY link supports both low-power data transmission and high-speed data transmission modes. Therefore, the RON of the switch should be balanced to optimize the performance of the hybrid operating mode. Ideally, this parameter should be set for each operating mode. Combining the best RON for each mode and keeping the switch CON very low is very important to maintain the slew rate at the receiving end. The general rule is that making CON lower than 10 pF will help avoid the deterioration (extension) of the signal transition time through the switch in high-speed mode.

As the MIPI interface architecture is gradually adopted by mobile platforms, designers may eventually eliminate the original parallel interface. Compared with previous generations of design, this alternative solution can save power, space and cost, while helping end customers increase productivity, and Bring them a more satisfying experience. The key to next-generation essential mobile design innovation is to take full advantage of the flexibility and functionality provided by processors and peripherals with MIPI capabilities.

Insulation PVC Fiberglass Sleeve

Insulation Pvc Fiberglass Sleeve,Pvc Coated Fiberglass Sleeve,Pvc Fiberglass Insulation Sleeve,Pvc Fiberglass Cable Sleeve

Longkou Libo Insulating Material Co.,Ltd. , https://www.sdliboinsulation.com