There are 5 exception modes in ARM and 7 interrupt sources. Some interrupts in these 7 interrupt sources are what we want to happen, but some interrupts are what we don't want to happen.

The interruption we want to happen:

Soft interrupt: belongs to the svc mode, and the soft interrupt can be generated through the SWI instruction and enter the svc mode.

irq interrupt: belongs to irq mode. When an ordinary external interrupt is generated, the processor enters the IRQ mode.

Fiq interrupt: belongs to fiq mode. When a high-priority external interrupt is generated, the processor enters the FIQ mode.

Disruptions we don’t want to happen:

Reset: It belongs to svc mode. When the system is powered on, a reset interrupt will be generated and the system enters svc mode. The reset interrupt does not require an interrupt return.

Instruction fetch abort interrupt: It belongs to abt mode. When the prefetch instruction error occurs, the instruction fetch abort interrupt is generated, and the abt mode is entered.

Data abort interrupt: belongs to abt mode. When accessing the data memory, a data abort interrupt is generated and enters abt mode.

Undefined instruction interrupt: belongs to the und mode. When an undefined instruction is executed, an undefined instruction interrupt is generated and the system enters the und mode.

The priority of the interrupt:

There are 6 priority levels in ARM. The priority order of each interrupt is as follows: (1 6 6s 5 2 4 3)

Reset: 1 data abort interrupt: 2fiq interrupt: 3irq interrupt: 4 prefetch address abort interrupt: 5 undefined instruction interrupt and soft interrupt: 6

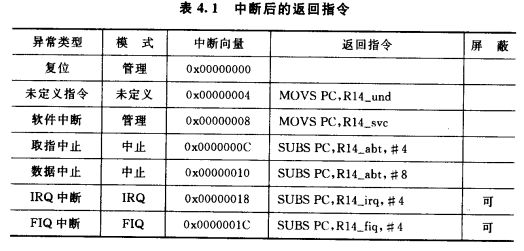

Regarding the problem of various interrupts that need to subtract a different offset from LR when the interrupt returns, I don’t think it is necessary to study in depth. This also involves the pipeline technology of ARM instructions. Usually interrupt code is written in C. Yes, there is no need to know this. You can check the meter when you use it.

The work done by the processor when entering an exception and exiting an exception:

When entering an exception:

1. Save the address to be returned in the LR corresponding to the abnormal mode. (Reset does not need to save the return address) 2. Copy the content of cpsr to the spsr corresponding to the abnormal mode. 3. Forcibly modify the content of cpsr, enter the corresponding abnormal mode and modify some bits as needed. 4. Force the PC to fetch the address from the corresponding interrupt vector address.

Note: The above steps are automatically completed by the cpu, that is, when an interrupt is generated, the hardware will automatically complete the above steps.

When exiting abnormally:

1. Assign the address saved in LR to PC. 2. Restore the content of spsr to cpsr. 3. Clear the irq interrupt disable bit.

Note: You only need to write a return instruction in the exception handler (as shown in Table 4.1 above) to achieve all the above steps.

Guangzhou Lufeng Electronic Technology Co. , Ltd. , https://www.lufengelectronics.com