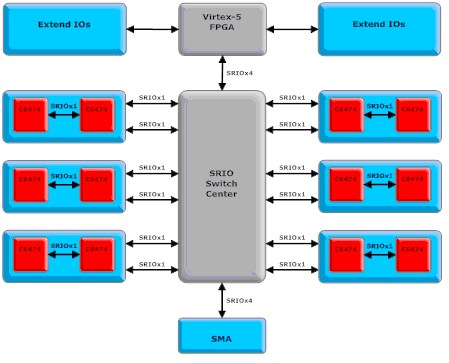

The development platform AVST_HSPP (High-speed Signal Processing Platform) is a multi-chip system based on Texas Instruments TMS320C6474 three-core high-performance DSP processor. The system uses a plug-in architecture and supports up to 12 motherboards. A DSP daughter card, each with a C6474 processor, 256MB of DDR2-667 high-speed memory and two 3.125Gbps SRIO high-speed interconnect serial buses. The system's motherboard uses the industry's high-performance SRIO high-speed data exchange chip, which can interconnect 12 DSPs and 1 Virtex-5 series of high-performance FPGAs to provide 80Gbps of on-board data exchange bandwidth. At the same time, the platform can also provide 12.5Gbps SRIO data exchange channel and 16Gbps extended IO data exchange channel to the outside.

This article refers to the address: http://

For multi-processor high-speed parallel computing systems, power consumption is critical, so while the system requires a significant increase in computing performance, multi-processor system architecture must be considered to control system power consumption in a relatively reasonable range. . Since the processor core power is proportional to the square of the main frequency, this means that the power consumption of three 1GHz processors is 30% of that of a 3GHz processor, and three of the TMS320C6474 processors can work. In the 1GHz/1.2GHz C64x+ high-performance DSP core, each DSP core has 92KB of L1 on-chip high-speed SRAM, three DSP cores share 3MB of L2 on-chip high-speed SRAM, and this processing is enabled by TI's unique SmartReflexTM technology. The industry has the industry's highest power efficiency of only 0.15mW per MIPS.

Chip interconnect, boot synchronization and multi-core communication and management are the biggest challenges in multi-processor system design. AVST's development platform chose SRIO bus as the physical interconnection between multiple processors, which is a high Performance multiprocessor interconnect, 1x mode can provide theoretical peaks up to 3.125Gbps with very little IO resources. The platform uses a high-performance SRIO switch chip as the data exchange center for 12 DSP processors and 1 FPGA chip. It can support 12 1x SRIO links and 2 4x SRIO data links. At the same time, with TI's CCS integrated development environment and DSP BIOS real-time kernel, accurate simulation and debugging of the three-core DSP program can be efficiently performed.

Multi-core multi-chip systems will become the mainstream solution for embedded mid- to high-end products. Avitech will continue to maintain a high strategic partnership with TI to provide customers with quality original design and solutions.

Liquid Crystal Display For Clock

Dongguan Yijia Optoelectronics Co., Ltd. , https://www.everbestlcdlcm.com